通過模態(tài)分析與S參數(shù)測試,識別背板諧振頻率及能量分布,優(yōu)化背板層壓結(jié)構(gòu)與接地過孔布局,降低25G/100G以太網(wǎng)系統(tǒng)的帶內(nèi)諧振噪聲,提升通信設(shè)備信道容量。

量化時鐘源至接收端的抖動傳遞函數(shù)(JTF),識別PLL、時鐘樹及電源噪聲對系統(tǒng)抖動的貢獻(xiàn),優(yōu)化時鐘架構(gòu)設(shè)計,滿足JEDEC標(biāo)準(zhǔn)對DDR5內(nèi)存時序精度的嚴(yán)苛要求。

針對CPO(光電共封裝)架構(gòu),分析電信號與光模塊間的耦合干擾路徑,優(yōu)化TIA/Driver電路與光纖接口的協(xié)同設(shè)計,滿足800G/1.6T光通信系統(tǒng)的混合信號完整性要求。

針對高速傳輸線的阻抗匹配需求,通過時域反射(TDR)技術(shù)分析路徑阻抗變化,定位PCB走線、連接器或過孔處的阻抗突變點(diǎn),降低信號反射與失真風(fēng)險,適用于PCIe/USB等高速接口設(shè)計驗(yàn)證。

驗(yàn)證SerDes芯片在PAM4/NRZ調(diào)制下的串行化與解串性能,優(yōu)化時鐘數(shù)據(jù)恢復(fù)(CDR)電路參數(shù),滿足AI訓(xùn)練芯片間互連的吞吐量需求。

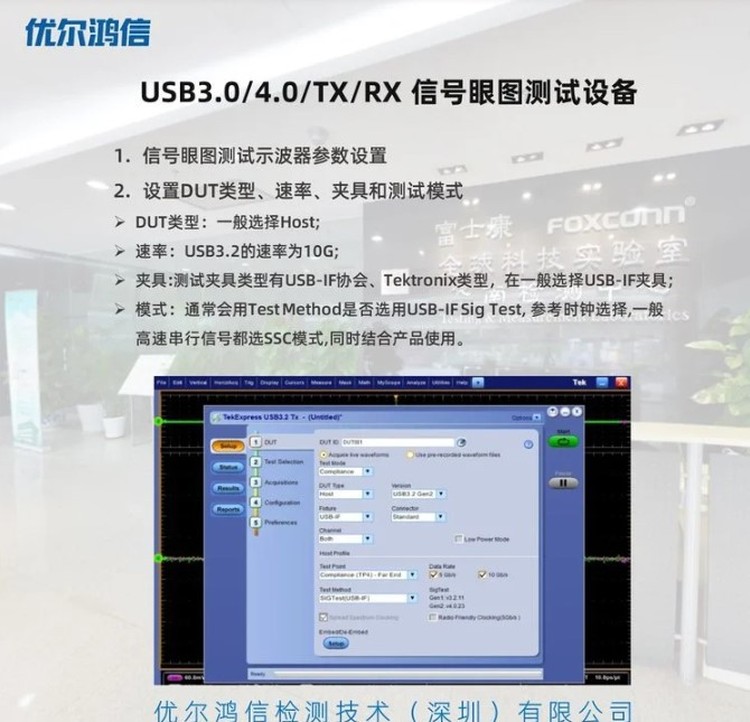

驗(yàn)證USB4/DP Alt Mode等多協(xié)議復(fù)用通道的信號完整性兼容性,優(yōu)化復(fù)用開關(guān)與阻抗切換電路設(shè)計,確保多功能接口的協(xié)議自適應(yīng)能力。